Document No.: FT\_000288 Clearance No.: FTDI #199

### Future Technology Devices International Ltd

### FT232H Single Channel Hi-Speed USB to Multipurpose UART/FIFO IC

The FT232H is a single channel USB 2.0 Hi-Speed (480Mb/s) to UART/FIFO IC. It has the capability of being configured in a variety of industry standard serial or parallel interfaces. The FT232H has the following advanced features:

- Single channel USB to serial / parallel ports with a variety of configurations.

- Entire USB protocol handled on the chip. No USB specific firmware programming required.

- USB 2.0 Hi-Speed (480Mbits/Second) and Full Speed (12Mbits/Second) compatible.

- Multi-Protocol Synchronous Serial Engine (MPSSE) to simplify synchronous serial protocol (USB to JTAG, I<sup>2</sup>C, SPI (MASTER) or bit-bang) design.

- UART transfer data rate up to 12Mbaud. (RS232 Data Rate limited by external level shifter).

- USB to asynchronous 245 FIFO mode for transfer data rate up to 8 Mbyte/Sec.

- USB to synchronous 245 parallel FIFO mode for transfers up to 40 Mbytes/Sec

- Supports a proprietary half duplex FT1248 interface with a configurable width, bidirectional data bus (1, 2, 4 or 8 bits wide).

- CPU-style FIFO interface mode simplifies CPU interface design.

- Fast serial interface option.

- FTDI's royalty-free Virtual Com Port (VCP) and Direct (D2XX) drivers eliminate the requirement for USB driver development in most cases.

- Adjustable receive buffer timeout.

- Option for transmit and receive LED drive signals.

- Bit-bang Mode interface option with RD# and WR# strobes

- Highly integrated design includes 5V to 3.3/+1.8V LDO regulator for VCORE, integrated POR function

- Asynchronous serial UART interface option with full hardware handshaking and modem interface signals.

- Fully assisted hardware or X-On / X-Off software handshaking.

- UART Interface supports 7/8 bit data, 1/2 stop bits, and Odd/Even/Mark/Space/No Parity.

- Auto transmit enable control for RS485 serial applications using the TXDEN pin.

- Operational mode configuration and USB Description strings configurable in external EEPROM over the USB interface.

- Configurable I/O drives strength (4, 8, 12 or 16mA) and slew rate.

- Low operating and USB suspend current.

- Supports self-powered, bus powered and highpower bus powered USB configurations.

- UHCI/OHCI/EHCI host controller compatible.

- USB Bulk data transfer mode (512 byte packets in Hi-Speed mode).

- +1.8V (chip core) and +3.3V I/O interfacing (+5V Tolerant).

- Extended -40°C to 85°C industrial operating temperature range.

- Compact 48-pin Lead Free LQFP or QFN package

- Configurable ACBUS I/O pins.

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied. Future Technology Devices International Ltd will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury. This document provides preliminary information that may be subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Future Technology Devices International Ltd, Unit 1, 2 Seaward Place, Centurion Business Park, Glasgow G41 1HH United Kingdom. Scotland Registered Company Number: SC136640

Document No.: FT\_000288 Clearance No.: FTDI #199

### 1 Typical Applications

- Single chip USB to UART (RS232, RS422 or RS485)

- USB to FIFO

- USB to FT1248

- USB to JTAG

- USB to SPI

- USB to I<sup>2</sup>C

- USB to Bit-Bang

- USB to Fast Serial Interface

- USB to CPU target interface (as memory)

- USB Instrumentation

- USB Industrial Control

- USB EPOS Control

- USB MP3 Player Interface

- USB FLASH Card Reader / Writers

- Set Top Box USB interface

- USB Digital Camera Interface

- USB Bar Code Readers

#### 1.1 Driver Support

The FT232H requires USB device drivers (listed below), available free from <a href="http://www.ftdichip.com">http://www.ftdichip.com</a>, to operate. The VCP version of the driver creates a Virtual COM Port allowing legacy serial port applications to operate over USB e.g. serial emulator application TTY. Another FTDI USB driver, the D2XX driver, can also be used with application software to directly access the FT232H through a DLL.

### Royalty free VIRTUAL COM PORT (VCP) DRIVERS for...

- Windows 10 and Windows 10 64-bit

- Windows 8 and Windows 8 64-bit

- Windows 7 and Windows 7 64-bit

- Windows Vista and Vista 64-bit

- Windows XP and XP 64-bit

- Windows XP Embedded

- Windows 2000, Server 2003, Server 2008

- Windows CE 4.2, 5.0, 5.2 and 6.0

- Mac OS-X

- Linux (2.6.39 or later)

### Royalty free D2XX *Direct* Drivers (USB Drivers + DLL S/W Interface)

- Windows 10 and Windows 10 64-bit

- Windows 8 and Windows 8 64-bit

- Windows 7 and Windows 7 64-bit

- Windows Vista and Vista 64-bit

- Windows XP and XP 64-bit

- Windows XP Embedded

- Windows 2000, Server 2003, Server 2008

- Windows CE 4.2, 5.0, 5.2 and 6.0

- Mac OS-X

- Linux (2.6.32 or later)

Document No.: FT\_000288 Clearance No.: FTDI #199

#### 1.2 Part Numbers

| Part Number   | Package     |

|---------------|-------------|

| FT232HL -xxxx | 48 Pin LQFP |

| FT232HQ-xxxx  | 48 Pin QFN  |

**Note:** Packaging codes for xxxx is:

Reel: Taped and Reel (LQFP = 1500 pieces per reel, QFN = 3000 pieces per reel)

Tray: Tray packing, (LQFP = 250 pieces per tray, QFN = 260 pieces per tray)

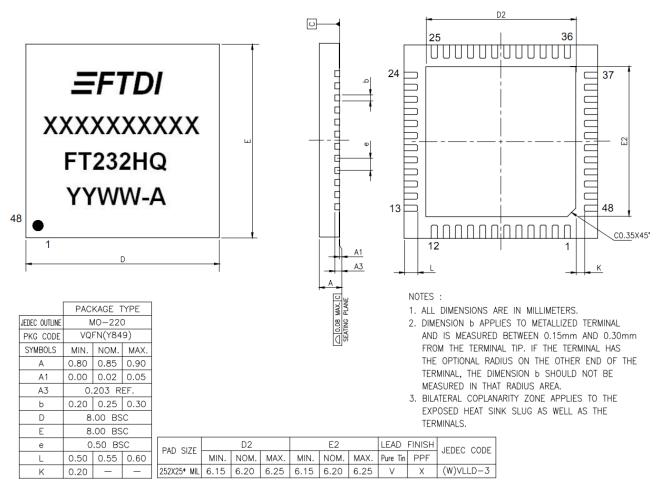

Please refer to section 8 for all package mechanical parameters.

### 1.3 USB Compliant

The FT232H is fully compliant with the USB 2.0 specification and has been given the USB-IF Test-ID (TID) 40770005.

The timing of the rise/fall time of the USB signals is not only dependant on the USB signal drivers, it is also dependant system and is affected by factors such as PCB layout, external components and any transient protection present on the USB signals. For USB compliance these may require a slight adjustment. This timing can be modified through a programmable setting stored in the same external EEPROM that is used for the USB descriptors. Timing can also be changed by adding appropriate passive components to the USB signals.

Document No.: FT\_000288 Clearance No.: FTDI #199

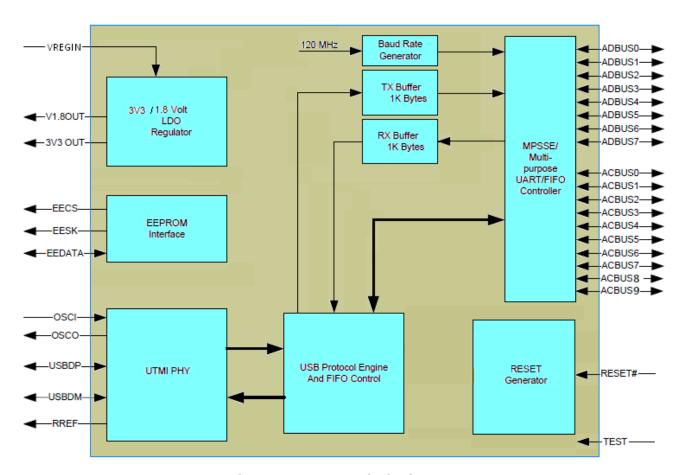

### 2 FT232H Block Diagram

Figure 2.1 FT232H Block Diagram

A full description of each function is available in section 4.

Document No.: FT\_000288 Clearance No.: FTDI #199

### **Table of Contents**

| 1 T   | ypical Applications                                      | 2    |

|-------|----------------------------------------------------------|------|

| 1.1   | Driver Support                                           | 2    |

| 1.2   | Part Numbers                                             | 3    |

| 1.3   | USB Compliant                                            | 3    |

| 2 F   | T232H Block Diagram                                      | 4    |

|       | Device Pin Out and Signal Descriptions                   |      |

| 3.1   | Schematic Symbol                                         |      |

| 3.2   | FT232H Pin Descriptions                                  |      |

|       |                                                          |      |

| 3.3   | Signal Description                                       |      |

| 3.4   | ACBUS Signal Option                                      |      |

| 3.5   | Pin Configurations                                       |      |

| 3.5.  | •                                                        |      |

| 3.5.  | ,                                                        |      |

| 3.5.  | , ,                                                      |      |

| 3.5.  | , ,                                                      |      |

| 3.5.  |                                                          |      |

| 3.5.  |                                                          |      |

| 3.5.  | ,                                                        |      |

| 3.5.8 | 5                                                        |      |

| 4 F   | unction Description                                      | 18   |

| 4.1   | Key Features                                             | . 18 |

| 4.2   | Functional Block Descriptions                            | . 19 |

| 4.3   | FT232 UART Interface Mode Description                    | . 20 |

| 4.3.  | 1 RS232 Configuration                                    | 20   |

| 4.3.  | 2 RS422 Configuration                                    | 21   |

| 4.3.  | RS485 Configuration                                      | 22   |

| 4.4   | FT245 Synchronous FIFO Interface Mode Description        | . 23 |

| 4.4.  | FT245 Synchronous FIFO Read Operation                    | 24   |

| 4.4.  | 2 FT245 Synchronous FIFO Write Operation                 | 24   |

| 4.5   | FT245 Style Asynchronous FIFO Interface Mode Description | . 25 |

| 4.6   | FT1248 Interface Mode Description                        | . 26 |

| 4.6.  | •                                                        |      |

| 4.6.  |                                                          |      |

| 4.7   | Synchronous and Asynchronous Bit-Bang Interface Mode     | . 29 |

Document No.: FT\_000288 Clearance No.: FTDI #199

| 4.7. | 1 Asynchronous Bit-Bang Mode              | 29 |

|------|-------------------------------------------|----|

| 4.7. | 2 Synchronous Bit-Bang Mode               | 29 |

| 4.8  | MPSSE Interface Mode Description          | 31 |

| 4.8. | 1 MPSSE Adaptive Clocking                 | 32 |

| 4.9  | Fast Serial Interface Mode Description    | 33 |

| 4.9. | 1 Outgoing Fast Serial Data               | 34 |

| 4.9. | 2 Incoming Fast Serial Data               | 34 |

| 4.9. | •                                         |    |

| 4.10 | CPU-style FIFO Interface Mode Description | 35 |

| 4.11 | RS232 UART Mode LDE Interface Description | 37 |

| 4.12 | Send Immediate/Wake Up (SIWU#)            | 38 |

| 4.13 | FT232H Mode Selection                     | 39 |

| 4.14 | Modes Configuration                       | 39 |

| 5 I  | Devices Characteristics and Ratings       | 40 |

| 5.1  | Absolute Maximum Ratings                  | 40 |

| 5.2  | DC Characteristics                        | 40 |

| 5.3  | ESD Tolerance                             | 42 |

| 6 F  | FT232H Configurations                     | 43 |

| 6.1  | USB Bus Powered Configuration             |    |

| 6.2  | USB Self Powered Configuration            | 44 |

| 6.2. | 1 Self-Powered Application Example 1      | 44 |

| 6.2. | .2 Self-Powered Application Example 2     | 45 |

| 6.3  | Oscillator Configuration                  | 46 |

| 7 E  | EEPROM Configuration                      | 47 |

| 7.1  | EEPROM Interface                          | 47 |

| 7.2  | Default EEPROM Configuration              | 47 |

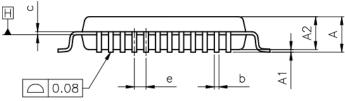

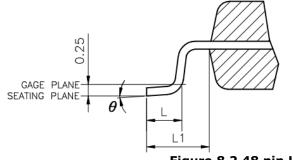

| 8 F  | Package Parameters                        | 49 |

| 8.1  | FT232HQ, QFN-48 Package Dimensions        | 49 |

| 8.2  | FT232HL, LQFP-48 Package Dimensions       | 50 |

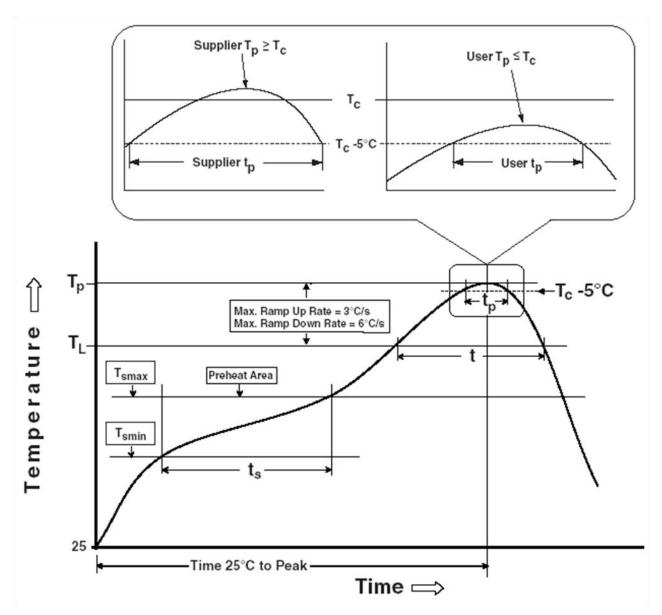

| 8.3  | Solder Reflow Profile                     | 51 |

| 9 (  | Contact Information                       | 53 |

|      | endix A – References                      |    |

|      | ument References                          |    |

|      | onyms and Abbreviations                   |    |

|      | <del>-</del>                              |    |

Document No.: FT\_000288 Clearance No.: FTDI #199

| Appendix B – List of Figures and Tables | 55 |

|-----------------------------------------|----|

| List of Tables                          | 55 |

| List of Figures                         | 56 |

| Appendix C – Revision History           | 57 |

Document No.: FT\_000288 Clearance No.: FTDI #199

### 3 Device Pin Out and Signal Descriptions

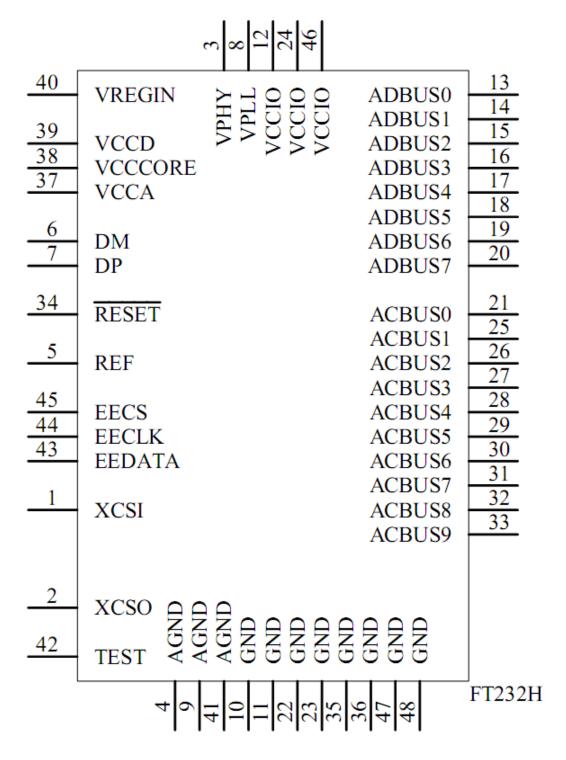

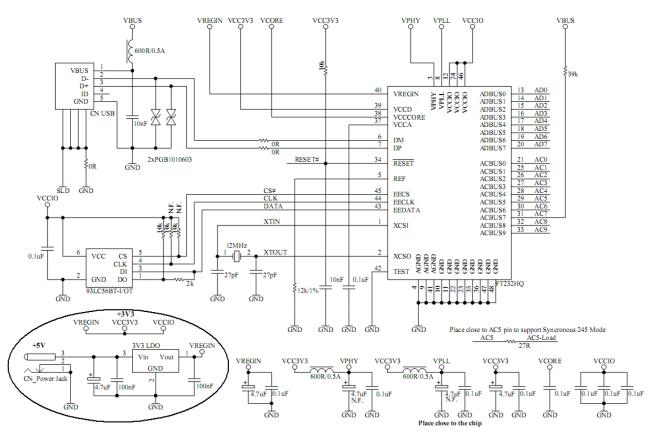

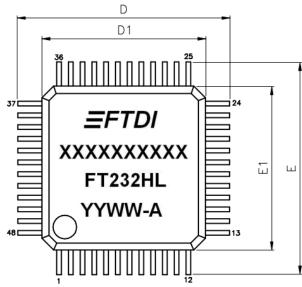

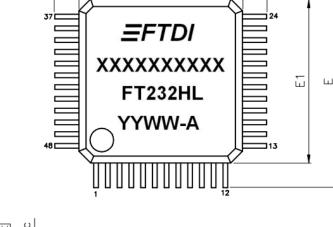

The 48-pin LQFP and 48-pin QFN have the same pin numbering for specific functions. This pin numbering is illustrated in the schematic symbol shown in Figure 3.1.

#### 3.1 Schematic Symbol

Figure 3.1 FT232H Schematic Symbol

Document No.: FT\_000288 Clearance No.: FTDI #199

#### 3.2 FT232H Pin Descriptions

This section describes the operation of the FT232H pins. Both the LQFP and the QFN packages have the same function on each pin. The function of many pins is determined by the configuration of the FT232H. The following table details the function of each pin dependent on the configuration of the interface. Each of the functions is described in the following table (Note: The convention used throughout this document for active low signals is the signal name followed by #).

|          | FT232H      |                                          |                     |                               |                   |                  |                  |                             |                      |             |

|----------|-------------|------------------------------------------|---------------------|-------------------------------|-------------------|------------------|------------------|-----------------------------|----------------------|-------------|

|          | Pin         | Pin functions (depends on configuration) |                     |                               |                   |                  |                  |                             |                      |             |

| Pin<br># | Pin<br>Name | ASYNC<br>Serial<br>(RS232)               | SYNC<br>245<br>FIFO | STYLE<br>ASYNC<br>245<br>FIFO | ASYNC<br>Bit-bang | SYNC<br>Bit-bang | MPSSE            | Fast<br>Serial<br>interface | CPU<br>Style<br>FIFO | FT1248      |

| 13       | ADBUS<br>0  | TXD                                      | D0                  | D0                            | D0                | D0               | TCK/SK           | FSDI                        | D0                   | MIOSI0      |

| 14       | ADBUS<br>1  | RXD                                      | D1                  | D1                            | D1                | D1               | TDI/DO           | FSCLK                       | D1                   | MIOSI1      |

| 15       | ADBUS<br>2  | RTS#                                     | D2                  | D2                            | D2                | D2               | TDO/DI           | FSDO                        | D2                   | MIOSI2      |

| 16       | ADBUS<br>3  | CTS#                                     | D3                  | D3                            | D3                | D3               | TMS/CS           | FSCTS                       | D3                   | MIOSI3      |

| 17       | ADBUS<br>4  | DTR#                                     | D4                  | D4                            | D4                | D4               | GPIOL0           | **<br>TriSt-UP              | D4                   | MIOSI4      |

| 18       | ADBUS<br>5  | DSR#                                     | D5                  | D5                            | D5                | D5               | GPIOL1           | **<br>TriSt-UP              | D5                   | MIOSI5      |

| 19       | ADBUS<br>6  | DCD#                                     | D6                  | D6                            | D6                | D6               | GPIOL2           | **<br>TriSt-UP              | D6                   | MIOSI6      |

| 20       | ADBUS<br>7  | RI#                                      | D7                  | D7                            | D7                | D7               | GPIOL3           | **<br>TriSt-UP              | D7                   | MIOSI7      |

| 21       | ACBUS<br>0  | *<br>TXDEN                               | RXF#                | RXF#                          | ACBUS0            | ACBUS0           | GPIOH0           | **<br>ACBUS0                | CS#                  | SCLK        |

| 25       | ACBUS<br>1  | **<br>ACBUS1                             | TXE#                | TXE#                          | WRSTB#            | WRSTB#           | GPIOH1           | **<br>ACBUS1                | A0                   | SS_n        |

| 26       | ACBUS<br>2  | **<br>ACBUS2                             | RD#                 | RD#                           | RDSTB#            | RDSTB#           | GPIOH2           | **<br>ACBUS2                | RD#                  | MISO        |

| 27       | ACBUS<br>3  | *<br>RXLED#                              | WR#                 | WR#                           | ACBUS3            | ACBUS3           | GPIOH3           | **<br>ACBUS3                | WR#                  | ACBUS3      |

| 28       | ACBUS<br>4  | *<br>TXLED#                              | SIWU#               | SIWU#                         | SIWU#             | SIWU#            | GPIOH4           | SIWU#                       | SIWU#                | ACBUS4      |

| 29       | ACBUS<br>5  | **<br>ACBUS5                             | CLKOUT              | ACBUS5                        | **<br>ACBUS5      | **<br>ACBUS5     | GPIOH5           | **<br>ACBUS5                | **<br>ACBUS<br>5     | ACBUS5      |

| 30       | ACBUS<br>6  | **<br>ACBUS6                             | OE#                 | ACBUS6                        | ACBUS6            | ACBUS6           | GPIOH6           | **<br>ACBUS6                | ** ACBUS 6           | ACBUS6      |

| 31       | ACBUS<br>7  | WRSAV#                                   | PWRSAV<br>#         | PWRSAV<br>#                   | PWRSAV<br>#       | PWRSAV<br>#      | ***<br>GPIOH7    | PWRSAV#                     | PWRSA<br>V#          | PWRSAV<br># |

| 32       | ACBUS<br>8  | **<br>ACBUS8                             | **<br>ACBUS8        | **<br>ACBUS8                  | **<br>ACBUS8      | **<br>ACBUS8     | **<br>ACBUS<br>8 | **<br>ACBUS8                | **<br>ACBUS<br>8     | ACBUS8      |

| 33       | ACBUS<br>9  | **<br>ACBUS9                             | **<br>ACBUS9        | **<br>ACBUS9                  | **<br>ACBUS9      | **<br>ACBUS9     | **<br>ACBUS<br>9 | **<br>ACBUS9                | **<br>ACBUS<br>9     | ACBUS9      |

Pins marked \* require an EEPROM for assignment to these functions. Default is Tristate, Pull-Up

Pins marked \*\* default to tri-stated inputs with an internal 75K $\Omega$  (approx.) pull up resistor to VCCIO.

Pin marked \*\*\* default to GPIO line with an internal  $75K\Omega$  pull down resistor to GND. Using the EEPROM this pin can be enabled USBVCC mode instead of GPIO mode.

Document No.: FT\_000288 Clearance No.: FTDI #199

### 3.3 Signal Description

The operation of the following FT232H pins are the same regardless of the configured mode:-

| Pin No.                 | Name         | Туре                        | Description                                                                                                                                                                                                                         |

|-------------------------|--------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40                      | **<br>VREGIN | POWER<br>input              | +5.0V or 3V3 power supply input.                                                                                                                                                                                                    |

| 37                      | VCCA         | POWER<br>output             | +1.8V output. Should not be used. Terminate with 0.1uF capacitor to GND                                                                                                                                                             |

| 38                      | VCORE        | POWER output                | +1.8V output. Should not be used. Terminate with a 0.1uF capacitor to GND                                                                                                                                                           |

| 39                      | **<br>VCCD   | POWER<br>output<br>or input | +3.3V output or input.                                                                                                                                                                                                              |

| 12, 24, 46              | VCCIO        | POWER input                 | +3.3V input. I/O interface power supply input                                                                                                                                                                                       |

| 8                       | VPLL         | POWER<br>Input              | +3.3V input. Internal PLL power supply input. It is recommended that this supply is filtered using an LC filter. (See figure 6.1)                                                                                                   |

| 3                       | VPHY         | POWER<br>Input              | +3.3V input. Internal USB PHY power supply input. Note that this cannot be connected directly to the USB supply. A +3.3V regulator must be used. It is recommended that this supply is filtered using an LC filter.(See figure 6.1) |

| 4,9,41                  | AGND         | POWER<br>Input              | 0V Ground input.                                                                                                                                                                                                                    |

| 10,11,22,23,35,36,47,48 | GND          | POWER<br>Input              | 0V Ground input.                                                                                                                                                                                                                    |

**Table 3.1 Power and Ground**

<sup>\*\*</sup> If pin 40 (VREGIN) is +5.0V, pin 39 becomes an output and If pin 40 (VREGIN) is 3V3 pin 39 becomes an input.

| Pin No. | Name    | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

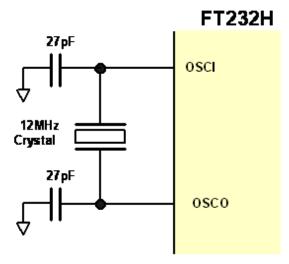

| 1       | OSCI    | INPUT  | Oscillator input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2       | OSCO    | OUTPUT | Oscillator output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5       | REF     | INPUT  | Current reference – connect via a 12K $\Omega$ resistor @ 1% to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 6       | DM      | I/O    | USB Data Signal Minus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7       | DP      | I/O    | USB Data Signal Plus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 42      | TEST    | INPUT  | IC test pin – for normal operation must be connected to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 34      | RESET#  | INPUT  | Reset input (active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 31      | PWRSAV# | INPUT  | USB Power Save input. This is an EEPROM configurable option which is set using a 'Suspend on ACBus7 Low' bit in FT_PROG. This option is available when the FT232H is on a self-powered mode and is used to prevent forcing current down the USB lines when the host or hub is powered off. PWRSAV# = 1 : Normal Operation PWRSAV# = 0 : FT232H forced into SUSPEND mode. PWRSAV# can be connected to VBUS of the USB connector (via a 39K $\Omega$ resistor). When this input goes high, then it indicates to the FT232H that it is connected to a host PC. When the host or hub is powered down then the FT232H is held in SUSPEND mode. |

**Table 3.2 Common Function Pins**

Document No.: FT\_000288 Clearance No.: FTDI #199

| Pin No. | Name   | Туре                                                                                                            | Description                                                                                                                                                                                                                        |

|---------|--------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

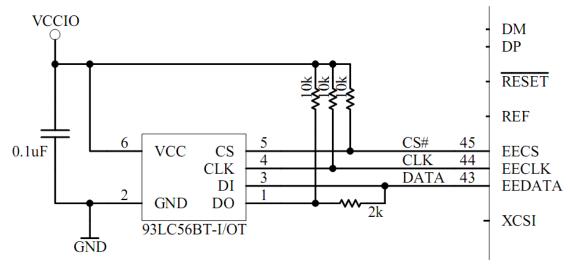

| 45      | EECS   | I/O                                                                                                             | EEPROM – Chip Select. Tri-State during device reset.                                                                                                                                                                               |

| 44      | EECLK  | OUTPUT Clock signal to EEPROM. Tri-State during device reset. When not in reset, this outputs the EEPROM clock. |                                                                                                                                                                                                                                    |

| 43      | EEDATA | I/O                                                                                                             | EEPROM – Data I/O. Connect directly to Data-in of the EEPROM and to Data-out of the EEPROM via a 2.2K resistor. Also, pull Data-Out of the EEPROM to VCCD via a 10K resistor for correct operation. Tri-State during device reset. |

**Table 3.3 EEPROM Interface Group**

| Pin No. | Name   | Туре   | Description                                                                                                                                                                                                                                           |  |

|---------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 13      | ADBUS0 | Output | Configurable Output Pin, the default configuration is Transmit Asynchronous Data Output.                                                                                                                                                              |  |

| 14      | ADBUS1 | Input  | Configurable Input Pin, the default configuration is Receiving Asynchronous Data Input.                                                                                                                                                               |  |

| 15      | ADBUS2 | Output | Configurable Output Pin, the default configuration is Request to Send Control Output / Handshake Signal.                                                                                                                                              |  |

| 16      | ADBUS3 | Input  | Configurable Input Pin, the default configuration is Clear To Send Control Input / Handshake Signal.                                                                                                                                                  |  |

| 17      | ADBUS4 | Output | Configurable Output Pin, the default configuration is Data Terminal Ready Control Output / Handshake Signal.                                                                                                                                          |  |

| 18      | ADBUS5 | Input  | Configurable Input Pin, the default configuration is Data Set Ready Control Input / Handshake Signal.                                                                                                                                                 |  |

| 19      | ADBUS6 | Input  | Configurable Input Pin, the default configuration is Data Carrier Detect Control Input.                                                                                                                                                               |  |

| 20      | ADBUS7 | Input  | Configurable Input Pin, the default configuration is Ring Indicator Control Input. When remote wake up is enabled in the EEPROM taking RI# low can be used to resume the PC USB host controller from suspend. (Also see note 1, 2, 3 in section 4.12) |  |

| 21      | ACBUS0 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 25      | ACBUS1 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 26      | ACBUS2 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 27      | ACBUS3 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 28      | ACBUS4 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 29      | ACBUS5 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 30      | ACBUS6 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 31      | ACBUS7 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PD. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 32      | ACBUS8 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

| 33      | ACBUS9 | I/O    | Configurable ACBUS I/O Pin. Function of this pin is configured in the device EEPROM. If the external EEPROM is not fitted the default configuration is TriSt-PU. See ACBUS Signal Options, Table 3.5.                                                 |  |

Table 3.4 UART Interface and ACBUS Group (see note 1)

Document No.: FT\_000288 Clearance No.: FTDI #199

#### **Notes:**

When used in Input Mode, the input pins are pulled to VCCIO via internal 75k $\Omega$  (approx.) resistors. These pins can be programmed to gently pull low during USB suspend (PWREN# = "1") by setting an option in the EEPROM.

### 3.4 ACBUS Signal Option

If the external EEPROM is fitted, the following options can be configured on the CBUS I/O pins using the software utility <u>FT\_PROG</u> which can be downloaded from the <u>FTDI utilities</u> page. CBUS signal options are common to both package versions of the FT232H. The default configuration is described in section 7.

| ACBUS<br>Signal<br>Option | Available On ACBUS Pin                                                       | Description                                                                                                                                                                                                                                                             |

|---------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXDEN                     | ACBUS0, ACBUS1, ACBUS2,<br>ACBUS3, ACBUS4, ACBUS5,<br>ACBUS6, ACBUS8, ACBUS9 | TXDEN = (TTL level). Used with RS485 level converters to enable the line driver during data transmit. TXDEN is active from one bit time before the start bit is transmitted on TXD until the end of the stop bit.                                                       |

| *PWREN#                   | ACBUS0, ACBUS1, ACBUS2,<br>ACBUS3, ACBUS4, ACBUS5,<br>ACBUS6, ACBUS8, ACBUS9 | Output is low after the device has been configured by USB, then high during USB suspend mode. This output can be used to control power to external logic P-Channel logic level MOSFET switch. Enable the interface pull-down option when using the PWREN# in this way.* |

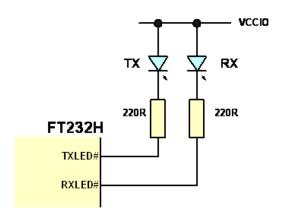

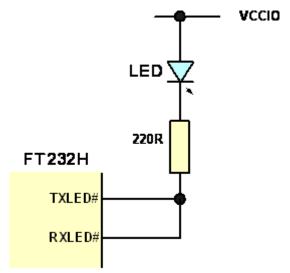

| TXLED#                    | ACBUS0, ACBUS1, ACBUS2,<br>ACBUS3, ACBUS4, ACBUS5,<br>ACBUS6, ACBUS8, ACBUS9 | TXLED = Transmit signalling output. Pulses low when transmitting data (TXD) to the external device. This can be connected to an LED.                                                                                                                                    |

| RXLED#                    | ACBUS0, ACBUS1, ACBUS2,<br>ACBUS3, ACBUS4, ACBUS5,<br>ACBUS6, ACBUS8, ACBUS9 | RXLED = Receive signalling output. Pulses low when receiving data (RXD) from the external device. This can be connected to an LED.                                                                                                                                      |

| TX&RXLED#                 | ACBUS0, ACBUS1, ACBUS2,<br>ACBUS3, ACBUS4, ACBUS5,<br>ACBUS6, ACBUS8, ACBUS9 | LED drive – pulses low when transmitting or receiving data from or to the external device.                                                                                                                                                                              |

| SLEEP#                    | ACBUSO, ACBUS1, ACBUS2,<br>ACBUS3, ACBUS4, ACBUS5,<br>ACBUS6, ACBUS8, ACBUS9 | Goes low during USB suspend mode. Typically used to power down an external TTL to RS232 level converter IC in USB to RS232 converter designs.                                                                                                                           |

| **CLK30                   | ACBUSO, ACBUS5,<br>ACBUS6,ACBUS8, ACBUS9                                     | 30MHz Clock output.                                                                                                                                                                                                                                                     |

| **CLK15                   | ACBUSO, ACBUS5,<br>ACBUS6,ACBUS8, ACBUS9                                     | 15MHz Clock output.                                                                                                                                                                                                                                                     |

| **CLK7.5                  | ACBUSO, ACBUS5,<br>ACBUS6,ACBUS8, ACBUS9                                     | 7.5MHz Clock output.                                                                                                                                                                                                                                                    |

| TriSt-PU                  | ACBUSO, ACBUS1, ACBUS2,<br>ACBUS3, ACBUS4, ACBUS5,<br>ACBUS6, ACBUS8, ACBUS9 | Input Pull Up                                                                                                                                                                                                                                                           |

| DRIVE 1                   | ACBUS0, ACBUS5,<br>ACBUS6,ACBUS8, ACBUS9                                     | Output High                                                                                                                                                                                                                                                             |

| DRIVE 0                   | ACBUSO, ACBUS1, ACBUS2,<br>ACBUS3, ACBUS4, ACBUS5,<br>ACBUS6, ACBUS8, ACBUS9 | Output Low                                                                                                                                                                                                                                                              |

| I/O mode                  | ACBUS5, ACBUS6,ACBUS8,<br>ACBUS9                                             | ACBUS Bit Bang                                                                                                                                                                                                                                                          |

**Table 3.5 ACBUS Configuration Control**

<sup>\*</sup> Must be used with a  $10k\Omega$  resistor pull up.

<sup>\*\*</sup>When in USB suspend mode the outputs clocks are also suspended.

Document No.: FT\_000288 Clearance No.: FTDI #199

#### 3.5 Pin Configurations

The following section describes the function of the pins when the device is configured in different modes of operation.

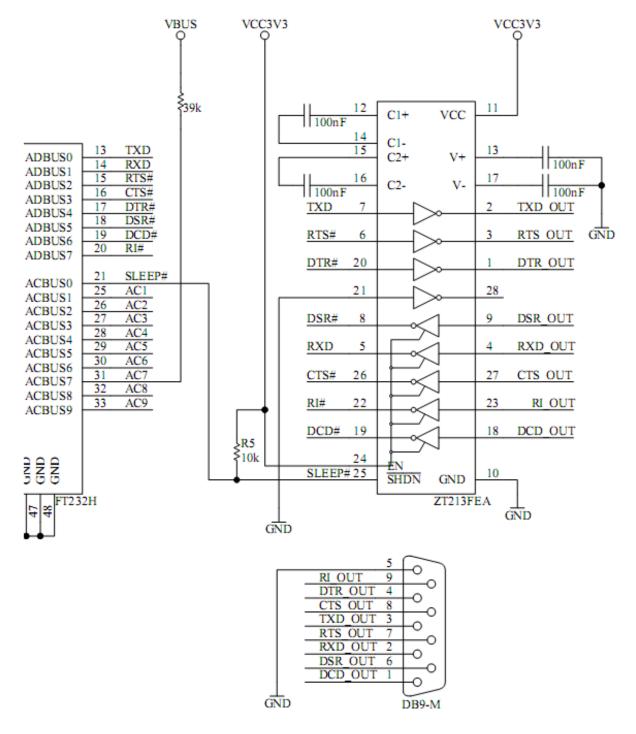

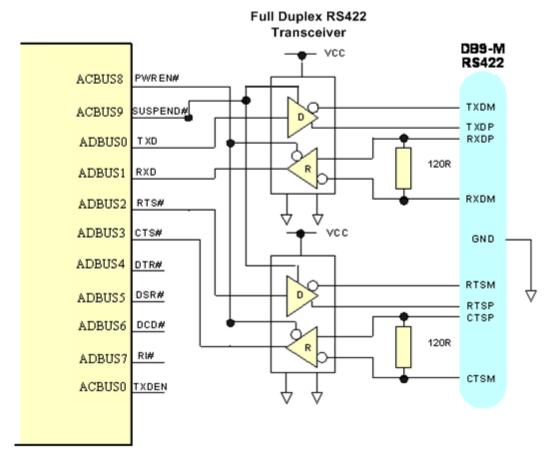

#### 3.5.1 FT232H pins used in an UART interface

The FT232H can be configured as a UART interface. When configured in this mode, the pins used and the descriptions of the signals are shown in Table 3.6.

| Pin<br>No. | Name        | Туре   | UART Configuration Description                                                                                                                                             |  |  |

|------------|-------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13         | TXD         | OUTPUT | TXD = transmitter output                                                                                                                                                   |  |  |

| 14         | RXD         | INPUT  | RXD = receiver input                                                                                                                                                       |  |  |

| 15         | RTS#        | OUTPUT | RTS# = Ready To send handshake output                                                                                                                                      |  |  |

| 16         | CTS#        | INPUT  | CTS# = Clear To Send handshake input                                                                                                                                       |  |  |

| 17         | DTR#        | OUTPUT | DTR# = Data Transmit Ready modem signalling line                                                                                                                           |  |  |

| 18         | DSR#        | INPUT  | DSR# = Data Set Ready modem signalling line                                                                                                                                |  |  |

| 19         | DCD#        | INPUT  | DCD# = Data Carrier Detect modem signalling line                                                                                                                           |  |  |

| 20         | RI#         | INPUT  | RI# = Ring Indicator Control Input. When the Remote Wake up option is enabled in the EEPROM, taking RI# low can be used to resume the PC USB Host controller from suspend. |  |  |

| 21         | **<br>TXDEN | OUTPUT | TXDEN = (TTL level). Use to enable RS485 level converter                                                                                                                   |  |  |

| 27         | **<br>RXLED | OUTPUT | RXLED = Receive signalling output. Pulses low when receiving data (RXD) from the external device (UART Interface). This should be connected to an LED.                     |  |  |

| 28         | **<br>TXLED | OUTPUT | TXLED = Transmit signalling output. Pulses low when transmitting data (TXD) to the external device (UART Interface). This should be connected to an LED.                   |  |  |

**Table 3.6 UART Configured Pin Descriptions**

For a functional description of this mode, please refer to section 4.3

**Note:** UART is the device default mode.

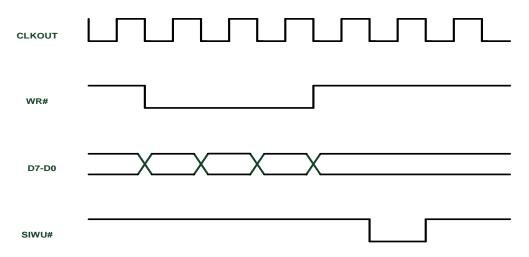

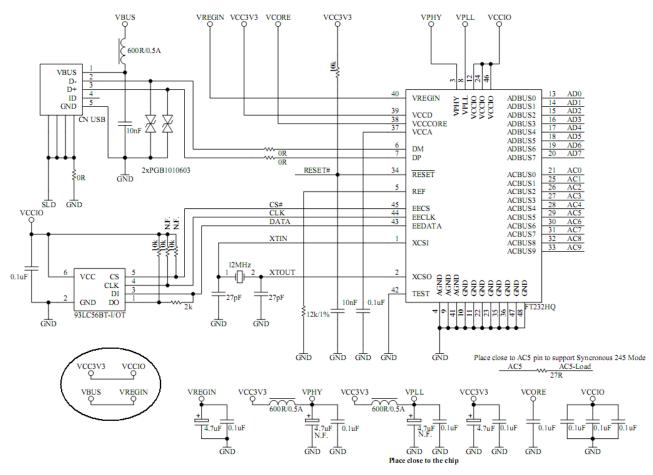

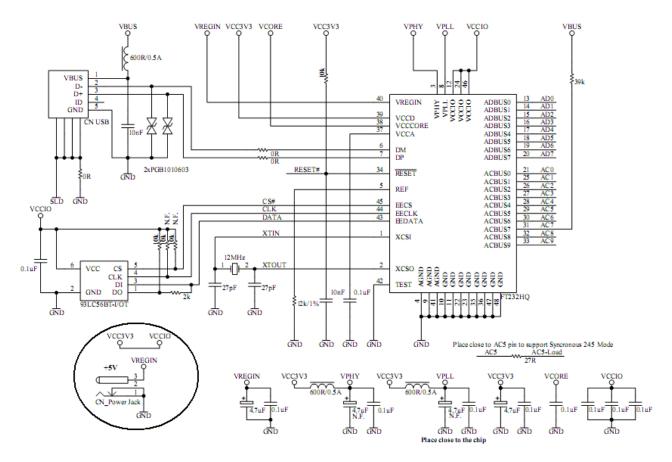

#### 3.5.2 FT232H Pins used in an FT245 Synchronous FIFO Interface

The FT232H can be configured as a FT245 synchronous FIFO interface. When configured in this mode, the pins used and the descriptions of the signals are shown in Table 3.7. To set this mode the external EEPROM must be set to 245 modes. A software command (FT\_SetBitMode) is then sent by the application to the FTDI D2XX driver to tell the chip to enter 245 synchronous FIFO mode. In this mode, data is written or read on the rising edge of the CLKOUT. Refer to Figure 4.4 for timing details.

| Pin No.                 | Name       | Туре   | FT245 Configuration Description                                                                                                                                                                                                                                                                                        |

|-------------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13,14,15,16,17,18,19,20 | ADBUS[7:0] | I/O    | D7 to D0 bidirectional FIFO data. This bus is normally input unless OE# is low.                                                                                                                                                                                                                                        |

| 21                      | RXF#       | OUTPUT | When high, do not read data from the FIFO. When low, there is data available in the FIFO which can be read by driving RD# low. When in synchronous mode, data is transferred on every clock that RXF# and RD# are both low. Note that the OE# pin must be driven low at least 1 clock period before asserting RD# low. |

| 25                      | TXE#       | OUTPUT | When high, do not write data into the FIFO. When low, data can be written into the FIFO by driving WR# low. When in synchronous mode, data is transferred on every clock that TXE# and WR# are                                                                                                                         |

<sup>\*\*</sup> ACBUS I/O pins

Document No.: FT\_000288 Clearance No.: FTDI #199

|    |             |        | both low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|----|-------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 26 | RD#         | INPUT  | Enables the current FIFO data byte to be driven onto D0D7 when RD# goes low. The next FIFO data byte (if available) is fetched from the receive FIFO buffer each CLKOUT cycle until RD# goes high.                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 27 | 7 WR#       |        | Enables the data byte on the D0D7 pins to be written into the transmit FIFO buffer when WR# is low. The next FIFO data byte is written to the transmit FIFO buffer each CLKOUT cycle until WR# goes high.                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 28 | SIWU#       | INPUT  | The Send Immediate / WakeUp signal combines two functions on a single pin. If USB is in suspend mode (PWREN# = 1) and remote wakeup is enabled in the EEPROM, strobing this pin low will cause the device to request a resume on the USB Bus. Normally, this can be used to wake up the Host PC.  During normal operation (PWREN# = 0), if this pin is strobed low any data in the device RX buffer will be sent out over USB on the next Bulk-IN request from the drivers regardless of the pending packet size. This can be used to optimize USB transfer speed for some applications. Tie this pin to VCCIO if not used. |  |  |  |

| 29 | CLKOUT      | OUTPUT | 60 MHz Clock driven from the chip. All signals should be synchronized to this clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 30 | 30 OE# INPU |        | Output enable when low to drive data onto D0-7. This should be driven low at least 1 clock period before driving RD# low to allow for data buffer turn around.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

Table 3.7 FT245 Synchronous FIFO Configured Pin Descriptions

For a functional description of this mode, please refer to section 4.4.

#### 3.5.3 FT232H Pins used in an FT245 Style aynchronous FIFO Interface

The FT232H can be configured as a FT245 style asynchronous FIFO interface. When configured in this mode, the pins used and the descriptions of the signals are shown in Table 3.8. To enter this mode the external EEPROM must be set to 245 asynchronous FIFO mode. In this mode, data is written or read on the falling edge of the RD# or WR# signals.

| Pin No.                          | Name       | Туре   | FT245 Configuration Description                                                                                                                                                                                                                                                                                                                              |  |  |

|----------------------------------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13, 14, 15, 16, 17,<br>18, 19,20 | ADBUS[7:0] | I/O    | D7 to D0 bidirectional FIFO data. This bus is normally input unless RD# is low.                                                                                                                                                                                                                                                                              |  |  |

| 21                               | RXF#       | OUTPUT | When high, do not read data from the FIFO. When low, there is data available in the FIFO which can be read by driving RD# low. When RD# goes high again RXF# will always go high and only become low again if there is another byte to read. During reset this signal pin is tristate, but pulled up to VCCIO via an internal $200 \text{k}\Omega$ resistor. |  |  |

| 25                               | TXE#       | OUTPUT | When high, do not write data into the FIFO. When low, data can be written into the FIFO by strobing WR# high, then low. During reset this signal pin is tristate, but pulled up to VCCIO via an internal $200k\Omega$ resistor.                                                                                                                              |  |  |

| 26                               | RD#        | INPUT  | Enables the current FIFO data byte to be driven onto D0D7 when RD# goes low. Fetches the next FIFO data byte (if available) from the receive FIFO buffer when RD# goes high.                                                                                                                                                                                 |  |  |

| 27                               | WR#        | INPUT  | Writes the data byte on the D0D7 pins into the transmit FIFO buffer when WR# goes from high to low.                                                                                                                                                                                                                                                          |  |  |

| SIWU# INPUT                      |            | INPUT  | The Send Immediate / WakeUp signal combines two functions on a single pin. If USB is in suspend mode                                                                                                                                                                                                                                                         |  |  |

Document No.: FT\_000288 Clearance No.: FTDI #199

| 28 | (PWREN# = 1) and remote wakeup is enabled in the EEPROM, strobing this pin low will cause the device to request a resume on the USB Bus. Normally, this can be used to wake up the Host PC.  During normal operation (PWREN# = 0), if this pin is strobed low any data in the device RX buffer will be sent out over USB on the next Bulk-IN request from the drivers regardless of the pending packet size. This can be used to optimize USB transfer speed for some |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | applications. Tie this pin to VCCIO if not used.                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 3.8 FT245 Style Asynchronous FIFO Configured Pin Descriptions

For a functional description of this mode, please refer to section 4.5.

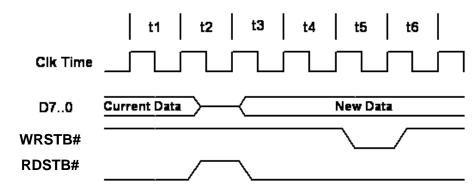

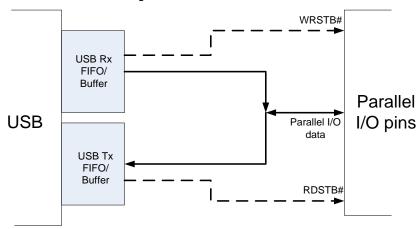

### 3.5.4 FT232H Configured as a Synchronous or Asynchronous Bit-Bang Interface

Bit-bang mode is an FTDI FT232H device mode that changes the 8 IO lines into an 8 bit bi-directional data bus. This mode is enabled by sending a software command (FT\_SetBitMode) to the FTDI driver. When configured in any bit-bang mode, the pins used and the descriptions of the signals are shown in Table 3.9

| Pin No.                               | Name   | Туре   | Configuration Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|---------------------------------------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13,14,15,16,17,18,19,20 ADBUS[7:0] I/ |        |        | D7 to D0 bidirectional Bit-Bang parallel I/O data pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 25                                    | WRSTB# | OUTPUT | Write strobe, active low output indicates when new data has been written to the I/O pins from the Host PC (via the USB interface).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 26                                    | RDSTB# | OUTPUT | Read strobe, this output rising edge indicates when data has been read from the parallel I/O pins and sent to the Host PC (via the USB interface).                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 28                                    | SIWU#  | INPUT  | The Send Immediate / WakeUp signal combines two functions on a single pin. If USB is in suspend mode (PWREN# = 1) and remote wakeup is enabled in the EEPROM, strobing this pin low will cause the device to request a resume on the USB Bus. Normally, this can be used to wake up the Host PC. During normal operation (PWREN# = 0), if this pin is strobed low any data in the device RX buffer will be sent out over USB on the next Bulk-IN request from the drivers regardless of the pending packet size. This can be used to optimize USB transfer speed for some applications. Tie this pin to VCCIO if not used. |  |  |

Table 3.9 Synchronous or Asynchronous Bit-Bang Configured Pin Descriptions

For functional description of this mode, please refer to section 4.6.

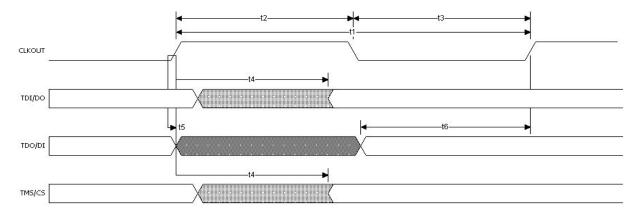

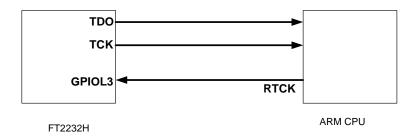

#### 3.5.5 FT232H Pins used in an MPSSE

The FT232H has a Multi-Protocol Synchronous Serial Engine (MPSSE). This mode is enabled by sending a software command (FT\_SetBitMode) to the FTDI D2xx driver. The MPSSE can be configured to a number of industry standard serial interface protocols such as JTAG, I²C or SPI (MASTER), or it can be used to implement a proprietary bus protocol. For example, it is possible to connect FT232H's to an SRAM configurable FPGA such as supplied by Altera or Xilinx. The FPGA device would normally not be configured (i.e. have no defined function) at power-up. Application software on the PC could use the MPSSE (and D2XX driver) to download configuration data to the FPGA over USB. This data would define the hardware function on power up. The MPSSE can be used to control a number of GPIO pins. When configured in this mode, the pins used and the descriptions of the signals are shown in Table 3.10

| Pin No. | Name   | Туре   | MPSSE Configuration Description                                       |  |

|---------|--------|--------|-----------------------------------------------------------------------|--|

| 13      | TCK/SK | OUTPUT | Clock Signal Output. For example:<br>JTAG – TCK, Test interface clock |  |

Document No.: FT\_000288 Clearance No.: FTDI #199

|    |        |        | SPI (MASTER) – SK, Serial Clock                                                                             |

|----|--------|--------|-------------------------------------------------------------------------------------------------------------|

| 14 | TDI/DO | OUTPUT | Serial Data Output. For example:<br>JTAG – TDI, Test Data Input<br>SPI (MASTER) – DO                        |

| 15 | TDO/DI | INPUT  | Serial Data Input. For example:<br>JTAG – TDO, Test Data output<br>SPI (MASTER) – DI, Serial Data Input     |

| 16 | TMS/CS | OUTPUT | Output Signal Select. For example:<br>JTAG – TMS, Test Mode Select<br>SPI (MASTER) – CS, Serial Chip Select |

| 17 | GPIOL0 | I/O    | General Purpose input/output                                                                                |

| 18 | GPIOL1 | I/O    | General Purpose input/output                                                                                |

| 19 | GPIOL2 | I/O    | General Purpose input/output                                                                                |

| 20 | GPIOL3 | I/O    | General Purpose input/output                                                                                |

| 21 | GPIOH0 | I/O    | General Purpose input/output                                                                                |

| 25 | GPIOH1 | I/O    | General Purpose input/output                                                                                |

| 26 | GPIOH2 | I/O    | General Purpose input/output                                                                                |

| 27 | GPIOH3 | I/O    | General Purpose input/output                                                                                |

| 28 | GPIOH4 | I/O    | General Purpose input/output                                                                                |

| 29 | GPIOH5 | I/O    | General Purpose input/output                                                                                |

| 30 | GPIOH6 | I/O    | General Purpose input/output                                                                                |

| 31 | GPIOH7 | I/O    | General Purpose input/output                                                                                |

**Table 3.10 MPSSE Configured Pin Descriptions**

For functional description of this mode, please refer to section 4.8.

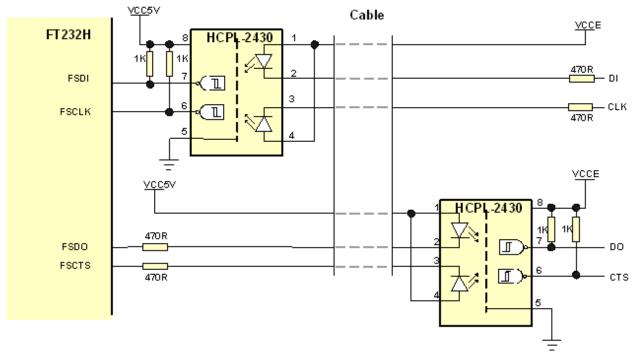

#### 3.5.6 FT232H Pins used as a Fast Serial Interface

The FT232H can be configured for use with high-speed bi-directional isolated serial data. A proprietary FTDI protocol designed to allow galvanic isolated devices to communicate synchronously with the FT232H using just 4 signal wires (over two dual opto-isolators), and two power lines. The peripheral circuitry controls the data transfer rate in both directions, whilst maintaining full data integrity. 12 Mbps (USB full speed) data rates can be achieved when using the proper high speed opto-isolators (see <a href="App Note AN-131">App Note AN-131</a>). When configured in this mode, the pins used and the descriptions of the signals are shown in Table 3.11.

| Pin<br>No. | Name  | Туре   | Fast Serial Interface Configuration Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13         | FSDI  | INPUT  | Fast serial data input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 14         | FSCLK | INPUT  | Fast serial clock input.<br>Clock input to FT232H chip to clock data in or out.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15         | FSDO  | OUTPUT | Fast serial data output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 16         | FSCTS | OUTPUT | Fast serial Clear To Send signal output. Driven low to indicate that the chip is ready to send data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28         | SIWU# | INPUT  | The Send Immediate / WakeUp signal combines two functions on a single pin. If USB is in suspend mode (PWREN# = 1) and remote wakeup is enabled in the EEPROM, strobing this pin low will cause the device to request a resume on the USB Bus. Normally, this can be used to wake up the Host PC. During normal operation (PWREN# = 0), if this pin is strobed low any data in the device RX buffer will be sent out over USB on the next Bulk-IN request from the drivers regardless of the pending packet size. This can be used to optimize USB transfer speed for some applications. Tie this pin to VCCIO if not used. |

**Table 3.11 Fast Serial Interface Configured Pin Descriptions**

For a functional description of this mode, please refer to section 4.9.

Document No.: FT\_000288 Clearance No.: FTDI #199

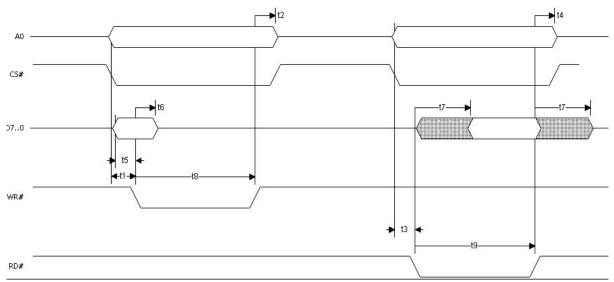

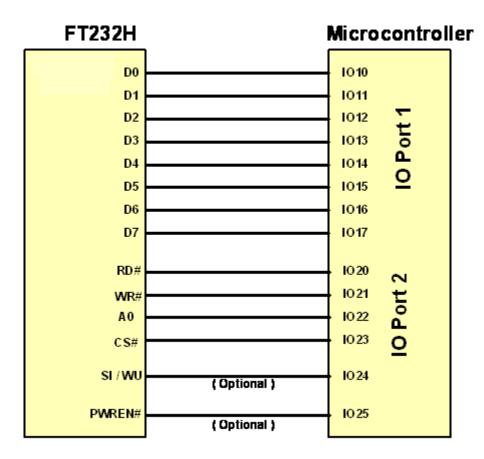

#### 3.5.7 FT232H Pins Configured as a CPU-style FIFO Interface

The FT232H can be configured in a CPU-style FIFO interface mode which allows a CPU to interface to USB via the FT232H. This mode is enabled in the external EEPROM. When configured in this mode, the pins used and the descriptions of the signals are shown in Table 3.12.

| Pin No.                                 | Name       | Туре  | Fast Serial Interface Configuration Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13, 14,<br>15, 16,<br>17, 18,<br>19, 20 | ADBUS[7:0] | I/O   | D7 to D0 bidirectional data bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 21                                      | CS#        | INPUT | Active low chip select input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 25                                      | A0         | INPUT | Address bit A0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 26                                      | RD#        | INPUT | Active Low FIFO Read input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

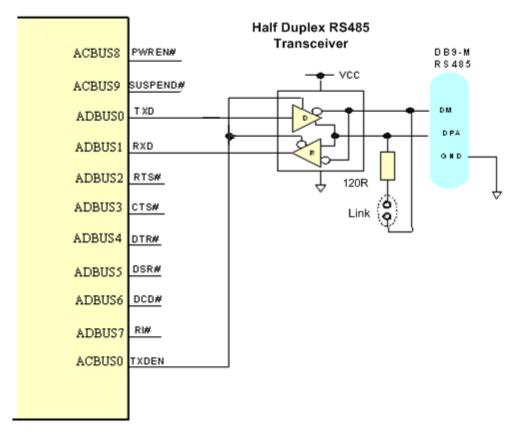

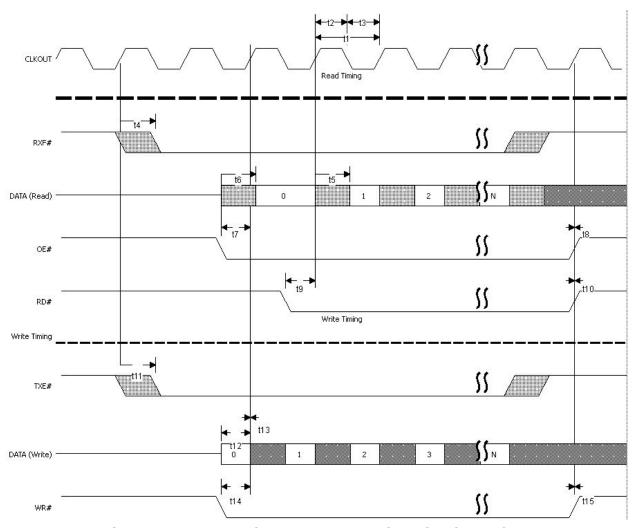

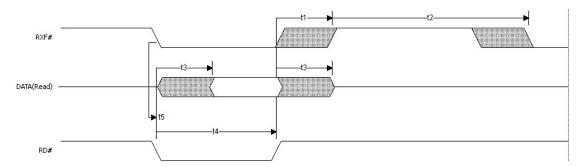

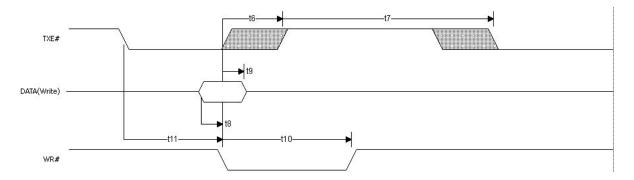

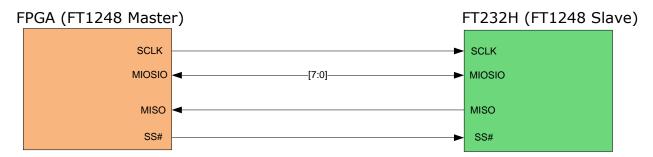

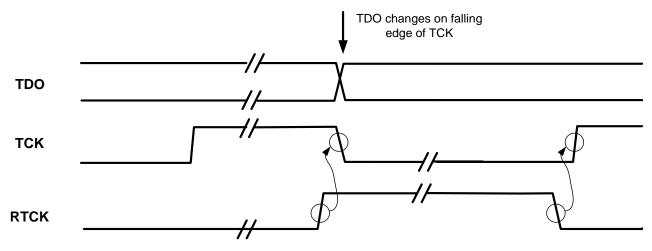

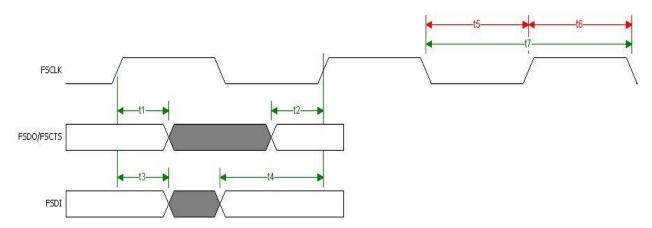

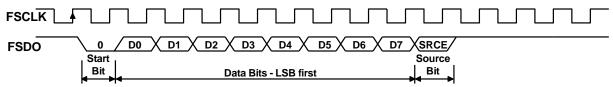

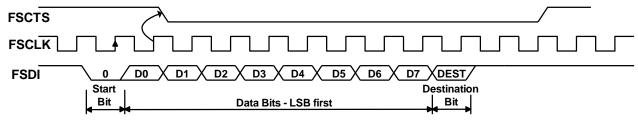

| 27                                      | WR#        | INPUT | Active Low FIFO Write input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |